您的位置:主页 > 公告动态 > 正大动态 > 正大动态

存储芯片蹊径图-外盘期货

CMOS 逻辑和存储器配合组成了半导体器件生产的绝大部门。本文思量的内存类型是 DRAM 和非易失性内存 (NVM)。重点是商品、自力芯片,由于这些芯片往往会推动内存手艺。然而,嵌入式存储芯片预计将遵照与商品存储芯片相同的趋势,通常会有一些时间滞后。对于 DRAM 和 NVM,都思量了详细的手艺要求和潜在的解决方案。

DRAM的生长偏向

对于 DRAM,主要目的是继续将 1T-1C 单元的封装尺寸扩大到 4F2 的现实极限。挑战在于垂直晶体管结构、高 κ 电介质以提高电容密度,同时保持低泄露。一样平常来说,DRAM 的手艺要求随着缩放而变得加倍难题。在已往的几年中,DRAM 引入了许多新手艺(例如,193 nm 氟化氩 (ArF) 浸没式High NA 光刻手艺和双图形手艺、改善的单元 FET 手艺,包罗鳍型晶体管、掩埋字线/单元 FET 手艺等等)。

由于 DRAM 存储电容器在物理上随着尺寸缩小而变小,因此等效氧化物厚度 (EOT) 必须急剧缩小以保持足够的存储电容。为了扩展 EOT,需要具有高相对介电常数 (κ) 的介电质料。因此,接纳高κ(ZrO2/Al2O/ZrO2)的金属-绝缘体-金属(MIM)电容器作为接地规则在48nm和30nm半间距之间的DRAM的电容器。和这个质料进化和改善一直延续到 20 nm HP 和超高 κ(钙钛矿 κ > 50~100)质料被释放。此外,高 κ 绝缘体的物理厚度应按比例缩小以顺应最小特征尺寸。因此,电容器的 3-D 结构将从圆柱形变为柱形。

另一方面,随着外围CMOS器件的微缩,这些器件形成后的工艺步骤需要低温工艺流程。这对于通常在 CMOS 器件形成后构建的 DRAM 单元工艺来说是一个挑战,因此仅限于低温处置。DRAM 外围装备要求可以放宽 Ioff 但需要更多 Ion 的低待机功耗 (LSTP) 装备。然则,在未来,将需要高 κ 金属栅极来维持性能。

另一个主要主题是从 6F2 到 4F2 cell的迁徙。由于半间距缩放变得异常难题,因此不能能维持成本趋势。保持成本趋势并逐代增添总比特输出的最有希望的方式是改变单元尺寸因子 (a) 缩放比例(其中 a = [DRAM 单元尺寸]/[DRAM 半间距])。现在 6F2(a = 6)是最常见的。例如,垂直单元晶体管是必须的,但仍然存在一些挑战。另一种选择是使用 3D DRAM。

总之,需要保持足够的存储电容和足够的单元晶体管性能以在未来保持保留时间特征。他们的难题要求正在增添,以继续扩展 DRAM 装备并获得更大的产物尺寸(即 >16 Gb)。除此之外,若是与引入新手艺相比,成本微缩的效率变差,那么DRAM微缩将会住手,而接纳3D单元堆叠结构,或者接纳新的DRAM观点。

Flash的演进方式

有几种交织的存储器手艺具有一个配合的特征——非易失性。要求和挑战因应用而异,局限从仅需要 Kb 存储的 RFID 到芯片中数百 Gb 的高密度存储。非易失性存储器可分为两大类——闪存(NAND Flash 和 NOR Flash)和非基于电荷的存储存储器。非易失性存储器基本上无处不在,许多应用程序使用通常不需要前沿手艺节点的嵌入式存储器。More Moore 非易失性存储器表仅跟踪前沿自力部件的存储器挑战和潜在解决方案。

闪存基于简朴的单晶体管 (1T) 单元,其中晶体管既用作接见(或单元选择)装备又用作存储节点。现在闪存服务于99%以上的应用。

当存储电子的数目到达统计极限时,纵然可以进一步缩小器件尺寸,实现更小的单元,存储器阵列中所有器件的阈值电压漫衍也变得不能控,逻辑状态不能展望。因此,存储密度不能通过延续缩放基于电荷的装备来无限增添。然而,通过垂直堆叠存储层可能会继续有用提高密度。

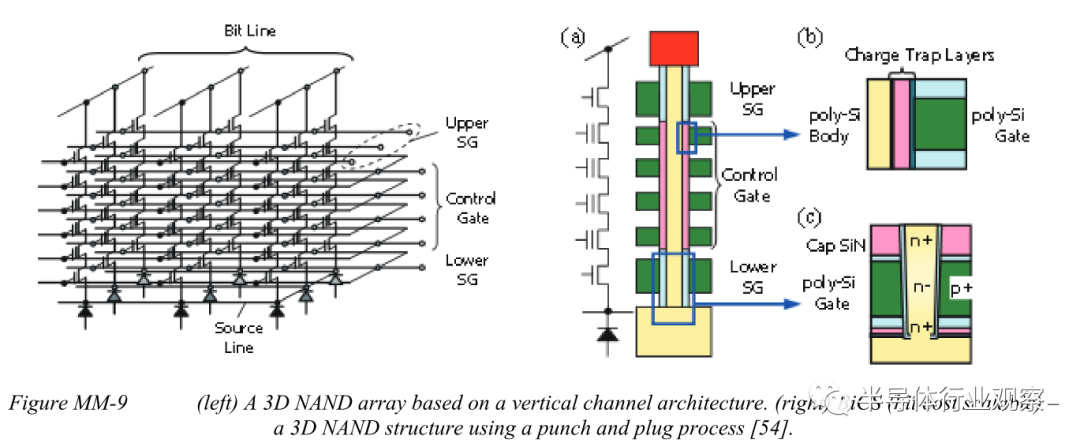

通过完成一个装备层然后完成另一层等等来堆叠的经济性值得嫌疑。如图 MM-9 所示,在堆叠几层装备后,每位成本最先上升。此外,由于庞大处置增添的互连和良率损失导致阵列效率下降,可能会进一步降低此类 3D 堆叠的每比特成本优势。

在2007 年,业内提出了一种“punch and plug”方式来垂直制造位线串,以大大简化加工步骤。这种方式使 3D 堆叠装备只需几个步骤,而不是通过重复处置,从而为 NAND 闪存提供了一条新的低成本扩展路径。图 MM-9 说明晰一种这样的方式。最初缔造的bit-cost-scalable(或 BiCS)架构将 NAND 串从水平位置转为垂直位置 90 度。字线(WL)保持在水平面上。如图 MM-9 所示,这种类型的 3D 方式比完整装备的堆叠要经济得多,而且成本效益不会到达相当高的层数。

自 2007 年以来,已经提出了许多基于 BiCS 观点的架构,当中包罗一些使用浮栅而不是电荷捕捉层举行存储的架构,这些手艺在已往 2-3 年中已经投入量产。一样平常来说,所有 3D NAND 方式都接纳了一种计谋,纵然用比传统 2D NAND 大得多的面积占用空间。3D NAND 的 x 和 y 尺寸(相当于 2D 中的单元尺寸)在 100nm 局限内甚至更高,而最小的 2D NAND 约为 15nm。更大的“单元尺寸”是通过堆叠大量存储层来实现具有竞争力的封装密度的。

3D NAND 的经济性因其庞大而怪异的制造需求而变得加倍杂乱。只管较大的单元尺寸似乎放宽了对细线光刻的要求,但要实现高数据速率,*使用large page size尺寸,而这又会转化为细间距位线和金属线。因此,纵然单元尺寸很大,金属线仍然需要约 20nm 的半间距,这只能通过具有双图案的 193i 光刻来实现。深孔刻蚀难度大、速率慢,刻蚀产量一样平常很低。沉积多层电介质和/或多晶硅,以及多层膜和深孔的计量都是对生疏领域的挑战。这些都转化为对新装备和占地面积的大量投资,以及对晶圆流和良率的新挑战。

最终的未知数是可以堆叠若干层。

层的堆叠似乎没有硬性物理限制。跨越一定的纵横比(也许是 100:1?)时,当反映离子蚀刻历程中的离子被侧壁上的静电荷弯曲而且不能进一步向下移动时,蚀刻住手(etch-stop)征象可能会限制一次操作中可以蚀刻的层数 . 然而,这可以通过堆叠更少的层、蚀刻和堆叠更多的层(以更高的成本)来绕过。

堆叠许多层可能会发生使晶圆弯曲的高应力,只管这需要仔细设计,但它似乎并不是无法解决的物理极限。纵然在 200 层(每层约 50nm)时,总堆叠高度约为 10µm,仍然与逻辑 IC 的 10-15 层金属层处于统一局限内。这种层厚度不会显着影响裸芯片厚度(现在最薄约为 40µm)。

然而,在 1000 层时,总层厚度可能会导致厚die不相符在薄封装中堆叠多个die(例如,16 或 32)的形状因数。现在量产176层,300 层有望实现,甚至500、800层也有可能。除了处置挑战之外,堆叠更多层还增添了接触更多字线所需的面积开销。该区域开销,加上增添的处置庞大性,最终将通过添加更多层来降低成本效益。

当堆叠更多层被证实太难题时,面积 x-y 足迹的重新缩小可能最终会最先。然而,这种趋势并不能保证。若是孔纵横比是限制因素,那么缩小占位面积不会降低该比率,因此也无济于事。此外,与慎密间距的 2D NAND 相比,更大的单元尺寸似乎至少部门有助于 3D NAND 的更好性能(速率和循环可靠性)。x-y 缩放是否仍能提供这样的性能尚不清晰。

因此,未来几代的蹊径图展望在 2022 年与当前节点保持一致。另一方面,增添每个存储单元的存储位数虽然在手艺上具有挑战性,但似乎取得了希望。这在一定水平上是为了行使 3D NAND 器件本质上更大,因此存储的电子更多,更容易制成更多的逻辑电平。

现在 4 位/单元器件 (QLC) 正在量产,而且乐观地以为 5 位/单元甚至更多可能在不久的未来变得可行。一个单元中更多的存储位需要在性能上做出一些折衷,由于它需要更长的时间来编程和读取,而且在将逻辑电平压缩在一起时可靠性会受到影响。然而对于许多读取麋集型应用程序来说,为了降低成本,这种权衡是可以接受的。

这个行业,高层出手整顿了

新兴存储的不确定性

由于存储电荷太少,2D NAND Flash 缩放受到统计颠簸的限制,一些不基于电荷存储的非通例非易失性存储器(铁电或 FeRAM、磁性或 MRAM、相变或 PCRAM,以及电阻或 ReRAM)正在开发中,形成通常称为“新兴”存储器的种别。

只管 2D NAND 正在被 3D NAND 取代(不再受制于电子太少的瑕玷),但基于非电荷的新兴存储器的一些特征(例如低电压操作或随机存取)正在被林林总总的应用关注从而获得继续生长的时机。这些新兴的存储器通常具有两头结构(例如,电阻器或电容器),因此很难同时用作单元格选择装备。存储单元一样平常以1T-1C、1T-1R或1D-1R的形式连系单独的存取器件。

FeRAM:铁随机存储器

FeRAM 器件通过切换和感测铁电电容器的极化状态来实现非易失性。要读取内存状态,必须跟踪铁电电容器的磁滞回线( hysteresis loop),而且存储的数据被损坏而且必须在读取后写回(损坏性读取,如 DRAM)。由于这种“损坏性读取”,找到既能提供足够的极化转变又能在延伸的事情周期内保持需要稳固性的铁电质料和电极质料是一项挑战。

许多铁电质料对于 CMOS 制造质料的正常弥补来说是生疏的,而且可以通过传统的 CMOS 处置条件退化。FeRAM 速率快、功耗低、电压低,因此适用于 RFID、智能卡、ID 卡和其他嵌入式应用。处置难度限制了它的普遍接纳。最近,提出了基于 HfO2的铁电 FET,其铁电性用于改变 FET 的 Vt,从而可以形成类似于闪存的 1T 单元。若是开发成熟,这种新存储器可以用作低功耗且速率异常快的类似闪存的存储器。

MRAM:磁性内存

MRAM (Magnetic RAM) 装备接纳磁性隧道结 (MTJ:magnetic tunnel junction) 作为存储元件。MTJ 单元由两种铁磁质料组成,由用作隧道势垒的薄绝缘层离隔。当一层的磁矩切换为与另一层对齐(或与另一层的偏向相反)时,电流流过 MTJ 的有用电阻会发生转变。可以读取隧道电流的巨细以指示存储的是“一”照样“零”。场切换 MRAM 可能是最靠近理想的“通用存储器”的,由于它是非易失性的、快速的而且可以无限循环。因此,它可以用作 NVM 以及 SRAM 和 DRAM。

然而,在 IC 电路中发生磁场既难题又低效。只管云云,Field Switching MTJ MRAM已经乐成制成产物。然而,当存储元件缩放时,切换所需的磁场会增添,而电迁徙会限制可用于发生更高 H 场的电流密度。因此,预计现场开关 MTJ MRAM 不太可能扩展到 65nm 节点以上。

“STT(spin-transfer torque )”方式的最新希望提供了一种新的潜在解决方案,其中自旋极化电流将其角动量转移到自由磁性层,从而在不借助外部磁场的情形下反转其极性。在自旋转移历程中,大量电流通过 MTJ 隧道层,这种应力可能会降低写入耐久性。在进一步缩放时,存储元件的稳固性会受到热噪声的影响,因此预计在 32nm 及以下需要垂直磁化质料。最近已经证实了垂直磁化。

随着NAND Flash的快速生长,以及最近推出的有望继续等效缩放的3D NAND,STT-MRAM取代NAND的希望似乎渺茫。然而,其类似 SRAM 的性能和比传统 6T-SRAM 小得多的占用空间在该应用中引起了极大的兴趣,稀奇是在不需要高循环耐久性的移动装备中,例如在盘算中。因此,STT-MRAM 现在大多不被视为自力内存,而是嵌入式内存 ,而且不在自力 NVM 表中举行跟踪。

STT-MRAM 不仅是嵌入式 SRAM 替换品的潜在解决方案,也是嵌入式闪存 (NOR) 替换品的潜在解决方案。这对于物联网应用来说可能稀奇有趣,由于低功耗是最主要的。另一方面,对于使用更高存储密度的其他嵌入式系统应用,预计 NOR 闪存将继续占有主导职位,由于它仍然更具成本效益。此外,闪存能够蒙受 PCB 板焊接历程(约 250°C)而不会丢失其预加载代码,这是众所周知的,许多新兴存储器尚未能够证实这一点。

PCRAM

PCRAM 器件使用硫属化物玻璃(最常用的化合物是 Ge2Sb2Te5,或 GST)的非晶态和晶态之间的电阻率差异来存储逻辑电平。该器件由顶部电极、硫族化物相变层和底部电极组成。泄露路径被与相变元件串联的存取晶体管(或二极管)切断。

相变写入操作包罗:(1) RESET,其中硫族化物玻璃通过短电脉冲瞬间熔化,然后快速淬火成具有高电阻率的非晶固体,以及 (2) SET,其中振幅较低但更长脉冲(通常 >100ns)将非晶相退火为低电阻晶态。1T-1R(或 1D-1R)单元比 NOR Flash 更大或更小,取决于使用的是 MOSFET 照样 BJT(或二极管。该装备可以被编程为任何最终状态而无需擦除先前状态,从而提供更快的编程吞吐量。简朴的电阻器结构和低电压操作也使 PCRAM 对于嵌入式 NVM 应用具有吸引力。

PCRAM 的主要挑战是重置相变元件所需的高电流(fraction of mA),以及相对较长的设置时间和高温耐受性以在回流焊时代(约 250°C)保留预加载代码。热滋扰是 PCRAM 可扩展性的潜在挑战。然而,热滋扰效应是非累积的(不像闪存,其中导致电荷注入的编程和读取滋扰是累积的)而且较高温度的RESET脉冲很短(10ns。相变质料与电极的相互作用可能会带来耐久的可靠性问题并限制循环耐久性,是类 DRAM 应用的主要挑战。与 DRAM 一样,PCRAM 是真正的随机存取、位可变存储器。

已经使用碳纳米管作为电极证实, PCRAM 器件可以做到 < 5nm 的可扩展性,而且复位电流遵照较大器件的外推线。至少在一个案例中,证实了 1E11 的循环耐力。相变存储器从2011年最先用于功效手机,取代NOR Flash,2012年最先在~45nm节点量产,但今后没有新产物推出。在已往的几年中,PCM 存储器也被瞄准为嵌入式应用程序的 eFlash 替换品的潜在候选者 。在这些事情中,差异种其余相变质料的合金化允许获得相符焊接回流的存储器;然而,云云高的温度稳固性是以较慢的写入速率为价值的。

ReRAM:电阻式存储器

现在正在研究一大类两头器件,其中存储状态由金属-绝缘体-金属 (MIM:metal-insulator-metal ) 结构的电阻率决议,用于存储应用。其中许多电阻式存储器仍处于研究阶段。由于他们准许缩小到 10nm 以下,并以极高的频率 (< ns) 和低功耗运行,已往十年中许多工业实验室的重点研发事情使这项手艺被普遍以为是 NAND 的潜在继续者(包罗 3D NAND ).

作为一种双端器件,高密度 ReRAM 的生长一直受到缺乏优越选择器器件的限制。然而,3D XP 内存的最新希望似乎已经解决了这个瓶颈,若是解决了不稳固位等其他手艺问题,ReRAM 可能会取得快速希望。除了 3D XP 阵列(类似于基于 PCRAM 的 3D XP 存储器)之外,还可以使用 2D 阵列和小字线 (WL) 和小位线 (BL) 半间距制造高密度 ReRAM 产物。

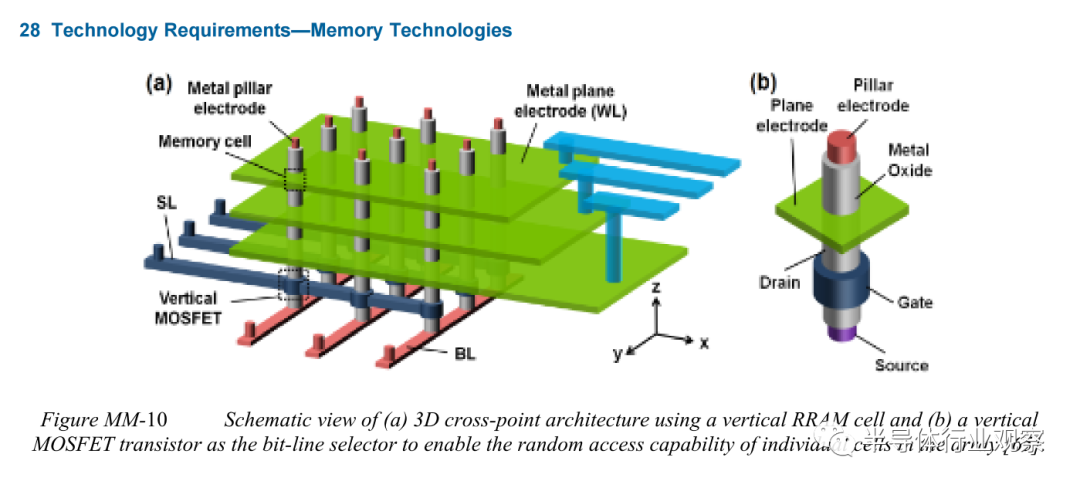

此外,若是最终接纳 OTS 类型的选择器器件,那么使用底部的晶体管和 3D 阵列中每个 ReRAM 器件的 OTS 选择器来制造 BiCS 型 3D ReRAM 似乎是可行的,如图 MM-10 所示。只管由于引入 3D XP 内存似乎解决了双极选择器装备的瓶颈,但尚未推出高密度 ReRAM 产物,但可以合理预期 ReRAM 的希望。

然而最近,开发高密度 ReRAM 的热情似乎消退了。这可能是由于两个缘故原由。(1) 3D NAND Flash的乐成增添了进入门槛, (2) 难以知足大型阵列的可靠性要求。(请注重,针对嵌入式应用程序的较小 Mb 巨细阵列乐成开发 ReRAM 已公布多项通告。)

在已往的几年中,上述这些问题似乎注定了高密度 ReRAM 的大规模应用。最初关于 ReRAM 由数千个原子组成,不受统计颠簸影响的论点现在看来值得嫌疑。似乎操作 ReRAM 的灯丝仅由几个原子(离子)组成。似乎有证据注释,纵然是相对较大的 ReRAM 装备也会受到统计颠簸的影响。因此,我们不看好高密度应用的 ReRAM。